Next-Generation SiC Transistors Claim World’s Lowest On-State Resistance

Sumitomo Electric Industries, Ltd. has developed V-groove superjunction transistors through a joint research project with the National Institute of Advanced Industrial Science and Technology (AIST) using silicon carbide (SiC) semiconductors, and has achieved the world's lowest on-state resistance of SiC transistors.

Sumitomo Electric has already developed V-groove metal-oxide-semiconductor field-effect transistors (VMOSFETs). The VMOSFETs use a particular plane orientation (0-33-8) for the channel that turns on/off the flow of electrons, forming an oxide film interface with low defects and achieving a low on-state resistance.

The low-defect performance of the transistors significantly stabilizes the threshold voltage fluctuation that prevents the practical use of SiC transistors. Sumitomo Electric is now working to commercialize VMOSFETs using the production line for 6-inch SiC wafers that AIST and Sumitomo Electric jointly built.

The resistance of the channel was reduced by introducing V-groove channel structure. Sumitomo Electric adopts a superjunction structure (illustrated above) for the further reduction of the on-state resistance. The superjunction structure is a technology to reduce the resistance of the withstand voltage layer (drift layer) and is commercialized for silicon transistors. However, it has remained in a principle verification stage for SiC transistor due to problems in manufacturing methods.

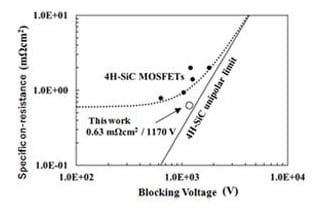

On-state resistance of SiC SJ-MOSFETs

On-state resistance of SiC SJ-MOSFETs

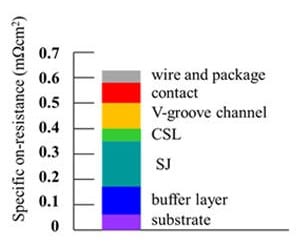

In this study, Sumitomo Electric overcame the problems by repeating epitaxial growth and ion implantation to form a narrow-pitch pillar structure and achieved the SiC superjunction structure for the VMOSFETs. By adopting the design and process optimized for the VMOSFET structure, which has low channel resistance, the new transistors have achieved a low on-state resistance of 1,170 V / 0.63 mΩ∙cm2.

Breakdown of the on-state resistance of SiC SJ-VMOSFETs

Breakdown of the on-state resistance of SiC SJ-VMOSFETs

These achievements of this study were reported at IEDM 2018 (IEEE International Electron Devices Meeting) in San Francisco, USA