Microchip's 750W ac-dc reference design demonstrates a semi-bridgeless PFC topology followed by a peak current controlled zero-voltage switching full-bridge (ZVS FB) converter with digital slope compensation to achieve very high conversion efficiencies.

This power supply can be firmware updated (including the compensator algorithm) with zero down time to the system it is powering while the power supply is running. It is implemented using two dsPIC33EP "GS" digital-power DSCs that provide full digital control of the power conversion as well as all system management functions.

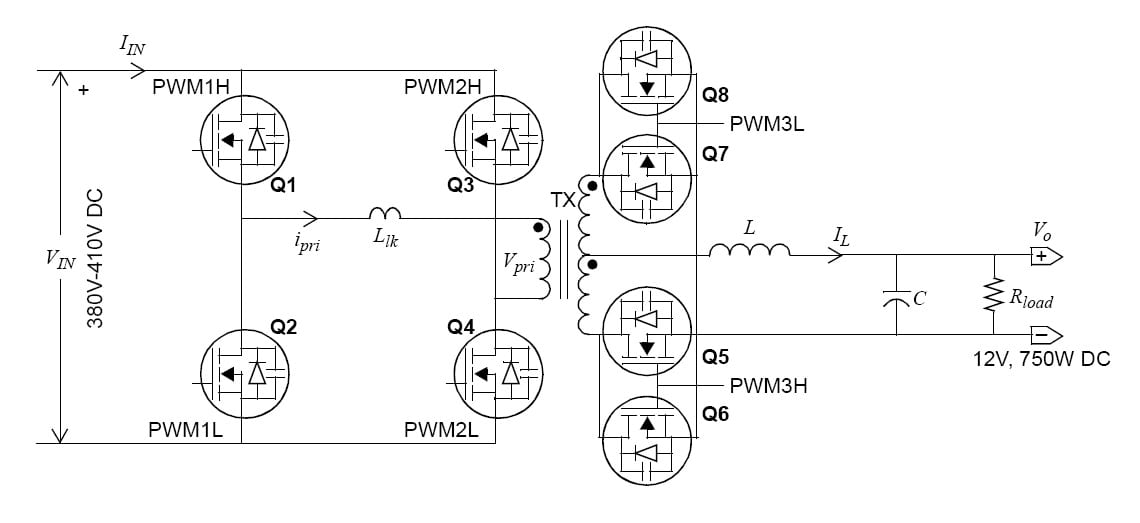

The ZVS FB Converter is designed to stepdown an input dc voltage of 400V to an output dc voltage of 12V. A unique feature of the reference design is the implementation of peak current control, using a fully software-based slope compensation algorithm, which eliminates the use of external analog components for slope compensation.

The ZVS FB Converter is one of the most commonly-used topologies in server and telecom power supplies, battery chargers and renewable applications, mainly due to its high-efficiency operation and ease of control. In this topology, both Average Current mode control and Voltage mode control implementations typically require a capacitor in series with the transformer to prevent flux walking.

Zero-Voltage Switching Full-Bridge (click on image to enlarge)

Zero-Voltage Switching Full-Bridge (click on image to enlarge)

The peak current control implementation eliminates the need for the series capacitor by virtue of dynamic flux balancing. In peak current control, however, to overcome the well-known subharmonic oscillations for duty cycles larger than 50%, a slope compensation ramp is either added to the inductor current or subtracted from the peak current reference generated by the voltage loop compensator.

Peak current control is typically an analog technique, implemented using linear amplifiers, transistors, RC networks and analog comparators, or by using dedicated ASICs.

Peak current control can also be accomplished digitally in three ways. The first method is popularly called predictive peak current control. In this technique, a leading-edge modulation of the PWM is used and the duty cycle is computed at the beginning of every cycle.

Peak Current-Mode Control - Analog (click on image to enlarge)

Peak Current-Mode Control - Analog (click on image to enlarge)

This technique eliminates the need for slope compensation and an analog comparator. Here, the effective duty cycle is calculated based on the inductance, sensed input and output voltages, and the switching period. The disadvantage of this method is the dependence on the inductance value, which is susceptible to variation.

The second method is essentially a hybrid technique, involving a digital compensator, analog slope compensation (external), and an analog comparator (internal to the microcontroller).

The hybrid technique consists of removing the analog compensator and replacing it with a digital compensator. The output of the compensator feeds a "digital peak current reference" to the Digital-to-Analog Converter (DAC) of a built-in high-speed analog comparator. The (internal) analog comparator then compares the DAC output to the slope compensated inductor current waveform and provides the truncation signal to the pwm module.

The inductor / switch current waveform is added to a slope compensation ramp using an external analog circuitry. In addition to requiring additional components, the analog slope compensation could be suboptimal for a wide input voltage range.

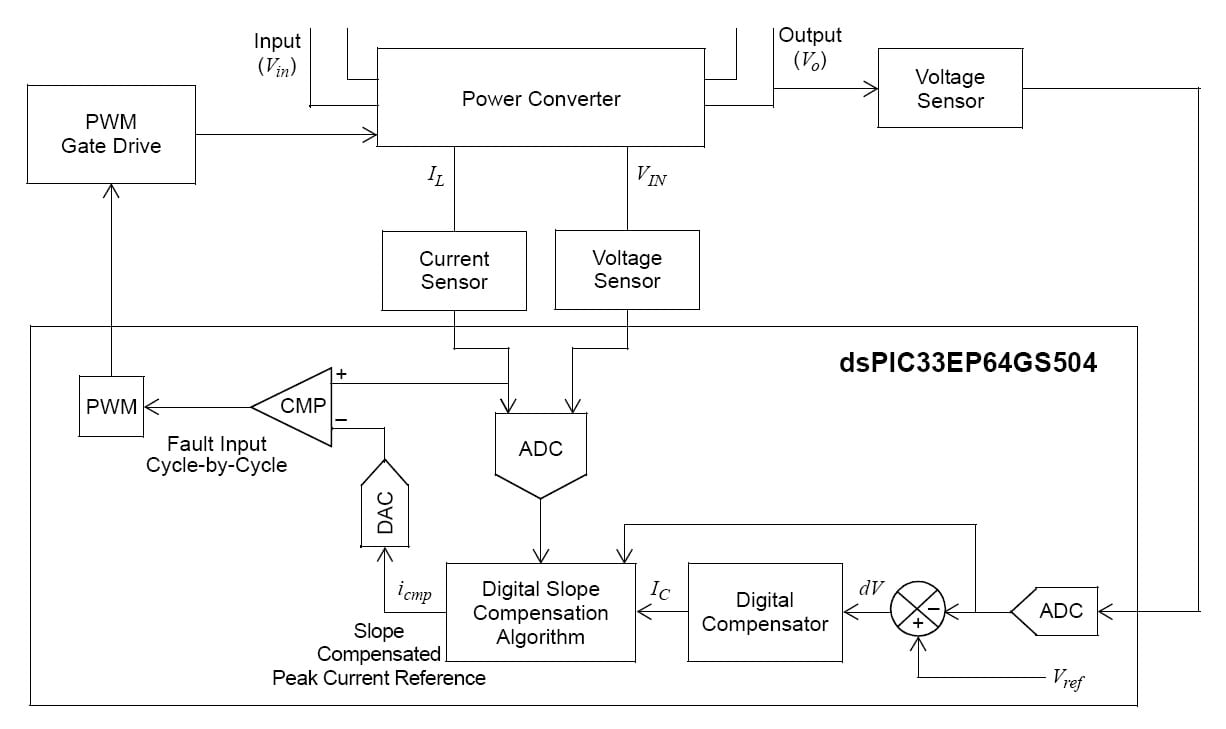

The third method which is used in this reference design is a fully-digital implementation, requiring no external components for implementing peak current control. The digital compensator, slope compensation and analog comparator are internal to the microcontroller. Here, the slope compensation is accomplished by an algorithm implemented in firmware.

Peak Current Control - Digital (click on image to enlarge)

Peak Current Control - Digital (click on image to enlarge)

This algorithm takes the input voltage, output voltage, inductor current and the digital peak current reference (from the digital compensator), and produces a slope compensated peak current reference.

The slope compensated peak current reference is then fed to the DAC of the internal high-speed comparator (inverting input). The inductor current feedback is fed directly to the non-inverting input of the comparator.

The advantages of this method are better reliability due to reduced components and the ability to implement adaptive algorithms for better dynamic response. A detailed discussion on the implementation of the fully digital peak current control is provided in corresponding application note.

The 750W ac-dc reference design is royalty free when used in accordance with the licensing agreement.