Factors Quantified for Reducing SiC MOSFET Resistance by Two-Thirds

A research group in Japan announced that it has quantified for the first time the impacts of three electron-scattering mechanisms for determining the resistance of silicon carbide (SiC) power semiconductor devices in power semiconductor modules.

The university-industry team consisting of researchers from the University of Tokyo and Mitsubishi Electric Corporation has found that resistance under the SiC interface can be reduced by two-thirds by suppressing electron scattering by the charges, a discovery that is expected to help reduce energy consumption in electric power equipment by lowering the resistance of SiC power semiconductors.

This research achievement was announced yesterday, December 4, at the 63rd International Electron Devices Meeting (IEDM) in San Francisco, California.

Electric power equipment used in home electronics, industrial machinery, trains and other apparatuses requires a combination of maximized efficiency and minimized size. Mitsubishi Electric is accelerating its use of SiC devices for power semiconductor modules.

SiC power devices offer lower resistance than conventional silicon power devices, so to further lower their resistance it is important to understand correctly the characteristics of the resistance under the SiC interface.

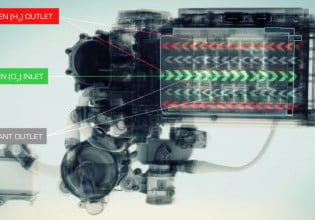

Electron scattering under the silicon carbide (SiC) interface is limited by three factors: roughness of the SiC interface, charges under the SiC interface and atomic vibration. (click on image to enlarge)

Electron scattering under the silicon carbide (SiC) interface is limited by three factors: roughness of the SiC interface, charges under the SiC interface and atomic vibration. (click on image to enlarge)

Satoshi Yamakawa

Satoshi Yamakawa

"Until now, however, it had been difficult to measure separately resistance-limiting factors that determine electron scattering," says Satoshi Yamakawa, senior manager of the SiC Device Development Center at Mitsubishi Electric's Advanced Technology R&D Center.

Electron scattering focusing on atomic vibration was measured using technology from the University of Tokyo. The impact that charges and atomic vibration have on electron scattering under the SiC interface was revealed to be dominant in Mitsubishi Electric's analyses of fabricated devices.

Although it has been recognized that electron scattering under the SiC interface is limited by three factors, namely, the roughness of the SiC interface, the charges under the SiC interface and the atomic vibration, the contribution of each factor had been unclear.

Impacts of resistance-limiting factors. (click on image to enlarge)

Impacts of resistance-limiting factors. (click on image to enlarge)

A planar-type SiC metal-oxide-semiconductor field-effect transistor (SiC-MOSFET), in which electrons conduct away from the SiC interface to around several nanometers, was fabricated to confirm the impact of the charges.

"We were able to confirm at an unprecedented level that the roughness of the SiC interface has little effect while charges under the SiC interface and atomic vibration are dominant factors," says Koji Kita, an associate professor at the University of Tokyo's Graduate School of Engineering and one of scientists leading the research.

Using an earlier planar-type SiC-MOSFET device for comparison, resistance was reduced by two-thirds owing to suppression of electron scattering, which was achieved by making the electrons conduct away from the charges under the SiC interface. The previous planar-type device has the same interface structure as that of the SiC-MOSFET fabricated by the electronics maker.

For the test, Mitsubishi Electric handled the design, fabrication and analysis of the resistance-limiting factors and the University of Tokyo handled the measurement of electron-scattering factors.

"Going forward, we will continue refining the design and specifications of our SiC MOSFET to further lower the resistance of SiC power devices," says Mitsubishi Electric's Yamakawa.