Automotive Data Flow Processor Test Chip Announced by NSITEXE

NSITEXE Inc. will join the 11th AUTOMOTIVE WORLD to be held at Tokyo Big Sight from Wednesday, January 16 to Friday, January 18, 2019. At the event, NSITEXE will unveil a test chip with a next-generation IP core (Data Flow Processor: DFP) that it is developing, as well as a test circuit board to be presented to potential customers and development partners.

This IP core is designed to realize a balance between performance and power, and also support the quality aspects that meet automotive standards.

Data flow architecture is a computer architecture that directly contrasts the traditional von Neumann architecture or control flow architecture. Data flow architectures do not have a program counter, or (at least conceptually) the executability and execution of instructions is solely determined based on the availability of input arguments to the instructions, so that the order of instruction execution is unpredictable: i.e. behavior is indeterministic.

Prior to this latest development by NSITEXE, data flow architecture has been successfully implemented in specialized hardware such as in digital signal processing, network routing, graphics processing, telemetry, and more recently in data warehousing. It is also very relevant in many software architectures today including database engine designs and parallel computing frameworks.

Synchronous data flow architectures tune to match the workload presented by real-time data path applications such as wire speed packet forwarding. Data flow architectures that are deterministic in nature enable programmers to manage complex tasks such as processor load balancing, synchronization and accesses to common resources.

Since being established in September 2017, NSITEXE has been building partnerships with companies including ThinCI Inc., a North American startup with key technology for high-performance semiconductors, to accelerate the development of the DFP.

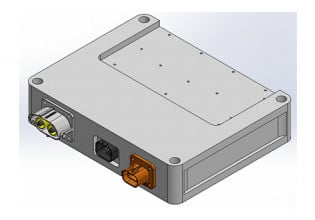

With an improved R&D system and in closer collaboration with partners including Dai Nippon Printing Co., Ltd., NSITEXE has developed a system on a chip (SoC) to demonstrate the performance of the DFP and a test circuit board on which to mount this SoC, and started trial production. Moreover, NSITEXE plans to start demonstration tests on the DFP, using the test chip and circuit board in the spring of 2019.

In addition to a DFP, the new SoC has two CPUs: Arm® Cortex®-R52 and Wave Computing MIPS I6500 and multiple interfaces, including LPDDR4 and PCIe. The performance of the DFP when used in a vehicle and when used with different embedded system applications will be demonstrated. A software development kit, drivers, a library, and other tools will be prepared and offered to development partners.

Demonstration tests are intended to improve the performance of next-generation DFPs and show to customers in different business fields how the DFP accelerates applications.